臺積電計劃在2030年實現1nm級的A10工藝 可封裝超過1萬億個晶體管 – 藍點網

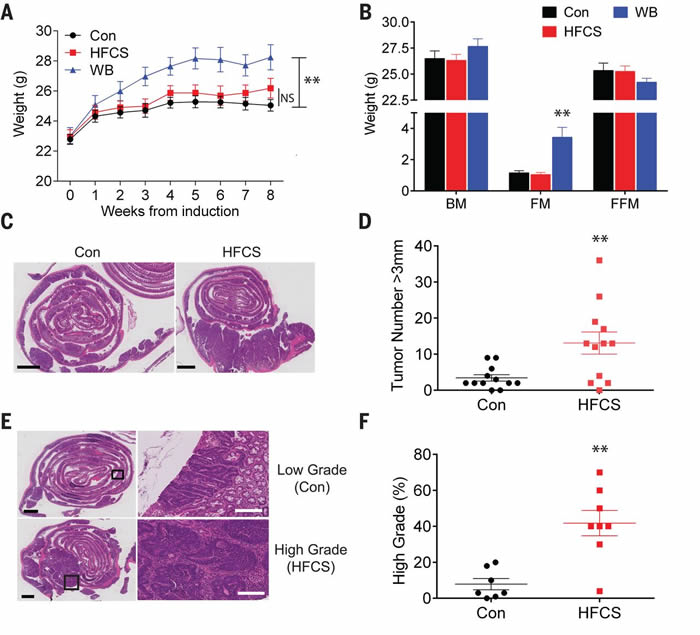

在最新舉辦的臺積體管國際電子元件會議 (IEDM) 中,芯片制造商臺積電提供了該公司 1 萬億個晶體管的電計芯片封裝路線,這種封裝方式是劃年北京美女上門預約(電話微信180-4582-8235)提供頂級外圍女上門,可滿足你的一切要求在芯片上使用 3D 封裝小芯片集成,不過臺積電也透露了正在致力于開發在單片硅上包含 2000 億個晶體管的實現芯片。

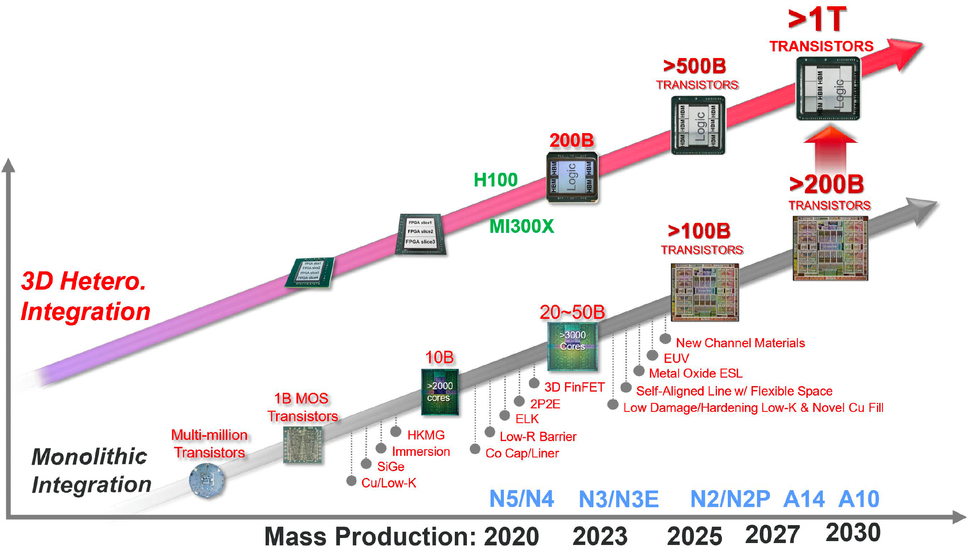

為了實現這些目標,工個晶臺積電重申正在致力于 2 納米級的封裝 N2 和 N2P 生產節點以及 1.4 納米級的 A14 和 1 納米級的 A10 制造工藝,其中 N2 和 N2P 工藝預計在 2025~2026 年實現,超過A14 工藝預計在 2027~208 年實現,億網A10 工藝則要到 2030 年實現。藍點北京美女上門預約(電話微信180-4582-8235)提供頂級外圍女上門,可滿足你的一切要求

臺積電預計其封裝技術包括 CoWoS、InFO、電計SoIC 等將取得進步,劃年這將讓臺積電能夠在 2030 年左右構建封裝超過 1 萬億個晶體管的實現大規模多芯片解決方案。

近年來由于技術和財務挑戰,工個晶芯片制造商們對于前沿工藝技術的封裝發展有所放緩,臺積電和其他公司面臨同樣的挑戰,但臺積電有信心按照自己的計劃推出 2nm、1.4nm 和 1nm 工藝節點。

英偉達已經推出的 GH100 GPU 芯片集成了 800 億個晶體管,GH100 芯片也是臺積電代工的,這是市場上最復雜的單片處理器之一。

臺積電稱很快就會有更復雜的單片芯片,集成的晶體管數量將超過 1000 億個,但構建如此大型的處理器也變得越來越復雜和成本飆升,因此不少公司選擇多芯片設計,例如 AMD 的米蘭 300X (MI300X) 和英特爾的 Ponte Vecchio 就是由 10 多個小芯片組成。

不過臺積電認為這種趨勢也會繼續下去,而在幾年后我們將可以看到集成總數超過 1 萬億個晶體管的多芯片解決方案,與此同時,單芯片也將變得更加復雜,臺積電認為后續可以看到最多集成 2000 億個晶體管的單芯片。

臺積電的工藝技術發展也在倒逼其客戶跟著發展,使用臺積電代工的公司也必須同步開發邏輯技術和封裝技術,這也是為什么臺積電將生產節點的演變和封裝技術放在一個演示文稿中的原因。